1. CONEXIÓN EN SERIE.

En este tipo de conexión la CPU sólo se conecta con la caché por lo que todas las peticiones que hace la CPU al bus del sistema son a través de la memoria caché.

Por lo tanto todo lo que necesita la CPU del sistema se lo proporciona la memoria caché y cómo es de tamaño y tiempo de acceso reducido cada vez que el dato está almacenado en la caché, el tiempo de acceso es muy reducido y evita manejar el bus del sistema.

Figura 1. Bloques del conexionado en serie

Fuente: (Angulo et all, 1995)

Si la memoria caché contiene el dato solicitado por la CPU, la parte superior de la figura 1 funcionará de manera independiente y en pocos nanosegundos proporcionará la información, liberando de la búsqueda a la parte inferior de la figura.

De esta forma si el bus del sistema está desocupado, simultáneamente que la CPU ejecuta instrucciones, los módulos de entrada/salida pueden estar trabajando con la memoria principal. Se permite el paralelismo.

1.1. DESVENTAJAS

El inconveniente de la conexión en serie es la penalización de tiempo ya que cuando la información que necesita la CPU no está en la caché tiene que trasladar la petición al bus del sistema para poder acceder a la memoria principal.

Otro inconveniente es que la caché es de uso obligatorio; no se puede desconectar la caché y conectar la CPU al sistema.

Cuando el bus del sistema queda libre, puede ser utilizado por todos los elementos que dependan de él.

2. ACCESO POR CONTENIDO

Cuando hablamos de acceso de contenido, en lo que se refiere la memoria caché, nos referimos a uno de los bloques del cual está conformado la caché, el BLOQUE DE ETIQUETAS: RAM-CAM, que es una memoria de acceso por contenido. No se accede por dirección de memoria, sino que, se compara el valor o dato con los que hay dentro de la memoria y así sabemos si se encuentra o no contenido en ella (Angulo et all, 1995)

3. LÓGICA DE CONTROL

El proceso del diseño lógico es una tarea compleja. La información binaria encontrada en un sistema digital se almacena en un procesador o registros de memoria y puede ser constituida por datos o información de control. Los datos son elementos discretos de información que son manipulados por micro operaciones. La información de control suministra señales de mandos para especificar la secuencia de micro operaciones. La lógica de diseño de un sistema digital es un progreso que sirve para deducir los circuitos digitales que realizan datos de procesamiento y de circuitos digitales que suministran señales de control.

La relación entre la unidad de control y el procesador de datos en un sistema digital se muestra en la Figura 2. La parte del procesador de datos puede ser una unidad procesadora de propósito general, o puede consistir en registros individuales y funciones digitales asociadas. El control se inicia con todas las micro operaciones en el procesamiento de datos. La lógica de control que genera señales para dar secuencia a las micro operaciones en un circuito secuencial está en función de control del sistema, para poder iniciar posteriormente con otras micro operaciones dependiendo de las condiciones presentes y otras entradas (Morris, 1982).

Figura 2. Interacción entre el control y el procesador de datos.

Fuente: (Morris, 1982)

3.1. REGISTRO DE SECUENCIA Y MÉTODO DEL DECODIFICADOR

Usa un registro para darle secuencia a los estados de control. El registro se decodifica para suministrar una salida en cada estado (Morris, 1982).

Figura 3. Lógica de control con un flip - flop por estado

Fuente: (Morris, 1982)

Figura 4. Lógica de control con registros de secuencia y decodificador.

Fuente: (Morris, 1982)

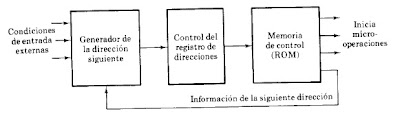

3.2. CONTROL DE MICROPROGRAMA

EL propósito de la unidad de control es iniciar una serie de pasos secuenciales de micro operaciones.

Figura 5. Lógica de control de microprograma

Fuente: (Morris, 1982)

Es muy importante las señales de control ya que nos especifican la dirección de la trasferencia que se va a realizar, es decir, cuando una palabra debe ser acumulada en un registro de memoria o cuando una palabra almacenada previamente debe ser transferida hacia afuera del registro de memoria (Morris, 1982).

4. EFICIENCIA

Cuando nos referimos en eficiencia, hacemos referencia al menor uso de recursos para poder conseguir un fin o funcionalidad requerida. Para poder obtener la eficiencia y mejor desempeño de la memoria caché, nos centramos en 2 técnicas para mejorar el rendimiento. Una se centra en reducir la tasa de fallos reduciendo la posibilidad de que dos bloques diferentes de memoria vayan a la misma posición de la caché. La segunda técnica reduce la penalización por fallo añadiendo un nivel adicional a la jerarquía de la memoria. Esta técnica es denominada Caché multinivel, apareció en las primeras máquinas de alto rendimiento. Todas estas técnicas con la finalidad de reducir los costes al acceso de la memoria caché (Morris, 1982).

5. REFERENCIAS BIBLIOGRÁFICAS

Angulo, J.M., Gutiérrez J.L., y Angulo I. (1995). Arquitectura de Microprocesadores: Los Pentium a fondo.Madrid: THOMSON PARANINFO, S.A.

Morris, M. Mano (1982). Lógica digital y diseño de Computadores. Editorial Prentice Hall. México

No hay comentarios:

Publicar un comentario