INTRODUCCION

La

tendencia histórica era diseñar procesadores cada vez más complejos y potentes,

que pudieran ejecutar muchas instrucciones diferentes, con muchos operandos y

muchos modos de direccionamiento. El objetivo de estos juegos de instrucciones

complejos era:

·

Facilitar el desarrollo de compiladores eficientes

·

Mejorar la eficiencia de la

ejecución, pues las instrucciones complejas se podían implementar

por microcódigo.

·

Dar soporte a

lenguajes de alto nivel más sofisticados.

·

Permitir la compatibilidad

entre familias de mainframes de un mismo fabricante.

DESARROLLO

IBM, tras analizar y estudiar

programas reales compilados, se dio cuenta que la mayoría de las instrucciones

de un programa son sencillas (asignaciones, operaciones aritméticas básicas...)

por lo que propusieron una arquitectura de procesador sencilla con muchos

registros de propósito general. Los ordenadores RISC, que ejecutara

eficientemente las instrucciones sencillas que son las más habituales, y las

complejas las descompusiera el compilador en operaciones más sencillas.

Una de las principales características de los RISC es

que las instrucciones son fácilmente segmentables, por lo que se consigue

finalizar una instrucción por ciclo de CPU. Pero existen límites en la mejora

del rendimiento que la segmentación puede conseguir:

·

Duración

del ciclo de reloj: El ciclo de reloj se puede reducir aumentando el número de

etapas, pero ello implica aumentar las dependencias, y con ello el CPI.

·

Velocidad

de búsqueda y decodificación de instrucciones: (cuello de botella de Flynn)

Sólo se pueden buscar unas pocas instrucciones por ciclo de reloj.

·

Cache

hits rate: Los programas científicos tienen con frecuencia conjuntos de datos

activos muy grandes, accedidos a menudo, con baja localidad, lo que da un

rendimiento bajo en la jerarquía de memoria, con muchas pérdidas en caché.

Los

procesadores escalares tienen un bajo rendimiento para ciertos tipos de

problemas matemáticos y de ingeniería donde los problemas se resuelven con

operaciones matriciales y vectoriales. Por ejemplo para multiplicar un vector

de 64 elementos por un escalar, un procesador escalar deberá hacer 64

operaciones dentro de un bucle. Claramente se observa que esta operación se

puede realizar de forma paralela para cada uno de los elementos del vector. Un

procesador vectorial podría realizar la operación sobre los vectores en una

sola instrucción sin necesidad de bucles.

Ahi es donde entran los procesadores

vectoriales que es

una CPU que ejecuta instrucciones que operan sobre un array unidimensional de

datos (un vector).

Una máquina vectorial consta de una

unidad escalar segmentada y una unidad vectorial. La unidad vectorial dispone

de M registros vectoriales de N elementos y de unidades funcionales vectoriales

(de suma, resta, multiplicación, división, de carga/almacenamiento,

etc) que trabajan sobre registros de ese tipo.

El juego de instrucciones de este tipo

de procesadores es evidentemente también vectorial. Un ejemplo de instrucción

vectorial sería addv v1,v2,v3, es decir, una operación vectorial que equivalen

a un bucle escalar completo que processaria los N elementos del registro vectorial.

La gran utilidad de crear CPUs

que tratan con vectores de datos

radica en la optimización de las tareas

que tiende a requerir una misma operación al ser

realizado con un gran conjunto de datos (por ejemplo, una suma o un producto

escalar).

Mientras que una CPU escalar debe

completar todo el proceso de leer, decodificar y ejecutar cada instrucción y

valor con un conjunto de datos, una CPU vectorial puede realizar una simple operació

con un conjunto relativamente grande de datos en una sola instrucción. Se

disminuye así tanto el ancho de banda de instrucciones requerido como el tiempo de decodificación.

Los procesadores

vectoriales son ampliamente utilizados actualmente en computación científica

(donde se demandan velocidades de cómputo muy elevadas), en aplicaciones de

predicción (meteorológica, de terremotos, de dinámica de fluídos, etc) así como

en las tarjetas gráficas que a su vez están incluidas en las consolas de videojuegos

más modernas de hoy en día.

Ventajas

del procesamiento vectorial:

- Permiten una gran segmentación pues los cálculos con cada elemento del vector suelen ser independientes.

- Cada instrucción vectorial equivale a un bucle, con los procesadores vectorial se evita tener que controlar el bucle.

- Las instrucciones vectoriales que acceden a memoria tienen un patrón de acceso predecible. Se puede organizar los datos en memoria entrelazadas para obtener un buen rendimiento de acceso a los datos.

Características

específicas de las máquinas vectoriales.

- Instrucciones especiales para operar vectores, incluidas dentro del juego de instrucciones del procesador.

- Registros separados para vectores y para escalares. Los procesadores vectoriales suelen tener un registro especial para indicar el número de elementos que componen el vector.

- Ejecución de las operaciones a través de segmentación, no hay varias unidades de ejecución paralelas.

- Necesidad de sistemas de memoria con un gran ancho de banda.

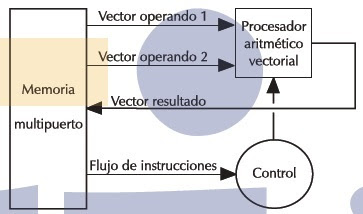

Fig.1, 2 RISC

vs PROCESADOR VECTORIAL

Fuente: (Callicó, 2004)

Fuente: (Callicó, 2004)

BIBLIOGRAFÍA Y PÁGINAS WEB

- Arquitectura de Computadoras y Procesamiento Paralelo. Kai Hwang y Fayé A. Briggs. McGraw-Hill, 1987.

- Computer Architecture, single and parallel systems. Mehdi R. Zargham. Prentice-Hall, 1996.

- Computer architecture: pipelined and parallel processor design. Michael J. Flynn. Jones and Bartlett, 1995.

- Organización y Arquitectura de Computadores, diseño para optimizar prestaciones. William Stallings. Prentice Hall, cuarta edición, 1996.

- See MIPS Run. D. Sweetman. Morgan Kaufmann Publications, 2002.

- Parallel Vector Processing; http://www.epcc.ed.ac.uk/HPCinfo/hware-pvp.html (HPC Info)

- Arquitectura de computadores; Julio Ortega, Mancia Anguita y Alberto Prieto (Thomson, 2004)